# Interleaved Buck Converter Having Low Switching Losses and Improved Step-Down Conversion Ratio

Il-Oun Lee, Student Member, IEEE, Shin-Young Cho, Student Member, IEEE, and Gun-Woo Moon, Member, IEEE

Abstract—This paper proposes a new interleaved buck converter (IBC) having low switching losses and improved step-down conversion ratio, which is suitable for the applications where the input voltage is high and the operating duty is below 50%. It is similar to the conventional IBC, but two active switches are connected in series and a coupling capacitor is employed in the power path, such as Cúk, Sepic, and Zeta converters. The proposed IBC shows that since the voltage stress across all the active switches is half of the input voltage before turn-on or after turn-off when the operating duty is below 50%, the capacitive discharging and switching losses can be reduced considerably. This allows the proposed IBC to have higher efficiency and operate with higher switching frequency. In addition, the proposed IBC has a higher step-down conversion ratio and a smaller output current ripple compared with a conventional IBC. The features, operation principles, and relevant analysis results of the proposed IBC are presented in this paper. The validity of this study is confirmed by the experimental results of prototype converters with 150–200 V input, 24 V/10 A output.

Index Terms-Buck converter, interleaved, low switching loss.

#### I. INTRODUCTION

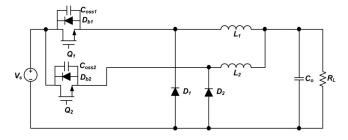

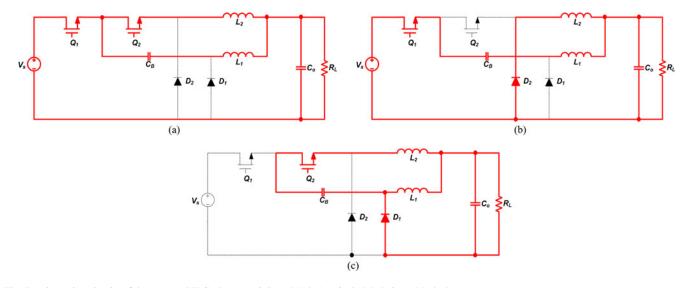

N APPLICATIONS where nonisolation, step-down conversion ratio, and high output current with low ripple are required, an interleaved buck converter (IBC) has received a lot of attention due to its simple structure and low control complexity [1]–[6]. However, in the conventional IBC shown in Fig. 1, all semiconductor devices suffer from the input voltage, and hence, high-voltage devices rated above the input voltage should be used. High-voltage-rated devices have generally poor characteristics such as high cost, high on-resistance, high forward voltage drop, severe reverse recovery, etc. In addition, the converter operates under hard switching condition. Thus, the cost becomes high and the efficiency becomes poor. And, for higher power density and better dynamics, it is required that the converter operates at higher switching frequencies [7]. However, higher switching frequencies increase the switching losses associated with turn-on, turn-off, and reverse recovery. Consequently, the efficiency is further deteriorated. Also, it experiences an extremely short duty cycle in the case of high-input and low-output voltage applications.

Fig. 1. Conventional IBC.

To overcome the aforementioned drawbacks of the conventional IBC, some pieces of research for reducing the voltage stress of a buck converter and several kinds of IBCs have been presented until now. In [8]-[10], three-level buck converters are introduced. The voltage stress is half of the input voltage in the converters. However, so many components are required for the use of IBC. In [11], an IBC with a single-capacitor turnoff snubber is introduced. Its advantages are that the switching loss associated with turn-off transition can be reduced, and single coupled inductor implements the converter as two output inductors. However, since it operates at discontinuous conduction mode (DCM), all elements suffer from high-current stress, resulting in high conduction and core losses. In addition, the voltages across all semiconductor devices are still the input voltage. In [12], an IBC with active-clamp circuits is introduced. In the converter, all active switches are turned ON with zero-voltage switching (ZVS). In addition, a high step-down conversion ratio can be obtained and the voltage stress across the freewheeling diodes can be reduced. However, in order to obtain the mentioned advantages, it requires additional passive elements and active switches, which increases the cost significantly at low or middle levels of power applications. In [13], an IBC with zero-current transition (ZCT) is introduced to reduce diode reverse recovery losses. The ZCT is implemented by only adding an inductor into the conventional IBC. However, in spite of these advantages, the converter suffers from high current stress, because the output current flows through each module in a complementary way. And it still has the drawbacks of the conventional IBC. An IBC with two winding coupled inductors is introduced in [14] and [15]. The converter has the following advantages. Since it operates at continuous conduction mode (CCM), the current stress is lower than that of DCM IBC. The voltages across all semiconductor devices can be reduced by adjusting the turn ratio of the coupled inductors, which allows that although it operates with hard switching, the switching losses can be reduced. Additionally, a high step-down conversion ratio can also be obtained.

Manuscript received February 8, 2011; revised May 18, 2011 and October 11, 2011; accepted January 12, 2012. Date of current version April 20, 2012. Recommended for publication by Associate Editor P. Jain.

The authors are with the School of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), Yuseong-Gu, Daejeon 305-701, Korea (e-mail: leeiloun@angel.kaist.ac.kr).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2012.2185515

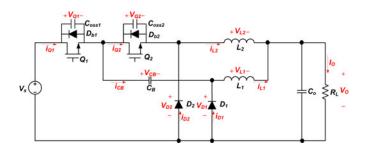

Fig. 2. Proposed IBC.

In this paper, a new IBC, which is suitable for the applications where the input voltage is high and the operating duty is below 50%, is proposed. It is similar to the conventional IBC, but two active switches are connected in series and a coupling capacitor is employed in the power path. The two active switches are driven with the phase shift angle of  $180^{\circ}$  and the output voltage is regulated by adjusting the duty cycle at a fixed switching frequency. The features of the proposed IBC are similar to those of the IBC in [14]. Since the proposed IBC also operates at CCM, the current stress is low. During the steady state, the voltage stress across all active switches before turn-on or after turn-off is half of the input voltage. Thus, the capacitive discharging and switching losses can be reduced considerably. The voltage stress of the freewheeling diodes is also lower than that of the conventional IBC so that the reverse-recovery and conduction losses on the freewheeling diodes can be improved by employing schottky diodes that have generally low breakdown voltages, typically below 200 V. The conversion ratio and output current ripple are lower than those of the conventional IBC.

The circuit operations of the proposed IBC are described in Section II in detail. The relevant analysis results are presented in Section III. The performance of the proposed IBC is confirmed by the experimental results of prototype converters with 150– 200 V input, 24 V/10 A output in Section IV. The conclusion is made in Section V.

# II. CIRCUIT OPERATIONS

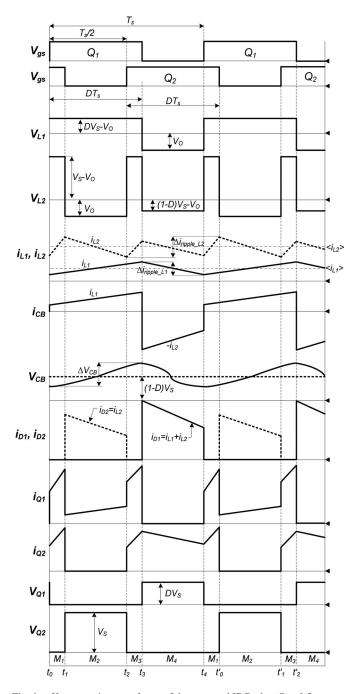

Fig. 2 shows the circuit configuration of the proposed IBC. The structure is similar to a conventional IBC except two active switches in series and a coupling capacitor employed in the power path. Figs. 3 and 6 show the key operating waveforms of the proposed IBC in the steady state. Referring to the figures, it can be seen that switches  $Q_1$  and  $Q_2$  are driven with the phase shift angle of 180°. This is the same as that for a conventional IBC. Each switching period is divided into four modes, whose operating circuits are shown in Figs. 4 and 5. In order to illustrate the operation of the proposed IBC, some assumptions are made as follows:

- 1) the output capacitor  $C_O$  is large enough to be considered as a voltage source;

- 2) the two inductors  $L_1$  and  $L_2$  have the same inductance L;

- 3) all power semiconductors are ideal;

- 4) the coupling capacitor  $C_B$  is large enough to be considered as a voltage source.

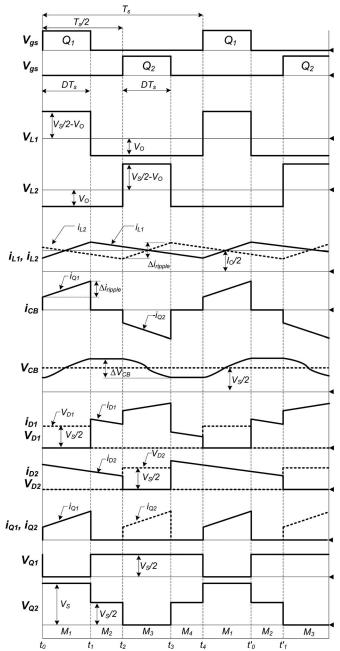

Fig. 3. Key operating waveforms of the proposed IBC when  $D \le 0.5$ .

### *A. Steady-State Operation when* $D \le 0.5$

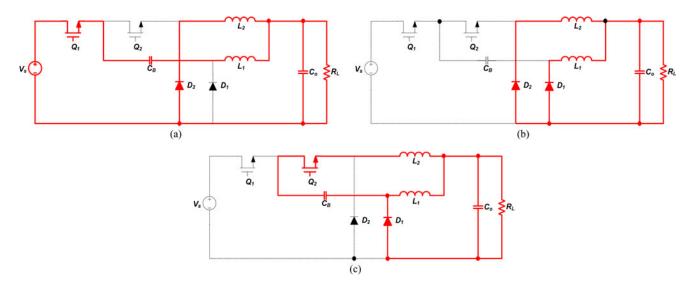

Mode 1  $[t_0-t_1]$ : Mode 1 begins when  $Q_1$  is turned ON at  $t_0$ . Then, the current of  $L_1$ ,  $i_{L1}(t)$ , flows through  $Q_1$ ,  $C_B$ , and  $L_1$  and the voltage of the coupling capacitor  $V_{CB}$  is charged. The current of  $L_2$ ,  $i_{L2}(t)$ , freewheels through  $D_2$ . During this mode, the voltage across  $L_1$ ,  $V_{L1}(t)$ , is the difference of the input voltage  $V_S$ , the voltage of the coupling capacitor  $V_{CB}$ , and the output voltage  $V_O$ , and its level is positive. Hence,  $i_{L1}(t)$  increases linearly from the initial value. The voltage across  $L_2$ ,  $V_{L2}(t)$ , is the negative output voltage, and hence,  $i_{L2}(t)$  decreases linearly from the initial value. The voltage across  $Q_2$ ,  $V_{Q2}(t)$ , becomes the input voltage and the voltage across  $D_1$ ,  $V_{D1}(t)$ , is equal to

Fig. 4. Operating circuits of the proposed IBC when  $D \le 0.5$ . (a) Mode 1. (b) Mode 2 or 4. (c) Mode 3.

Fig. 5. Operating circuits of the proposed IBC when D > 0.5. (a) Mode 1 or 3. (b) Mode 2. (c) Mode 4.

the difference of  $V_S$  and  $V_{CB}$ . The voltages and currents can be expressed as follows:

$$V_{L1}(t) = V_S - V_{CB} - V_O$$

(1)

$$V_{L2}(t) = -V_O \tag{2}$$

$$i_{L1}(t) = \frac{V_S - V_{CB} - V_O}{L}(t - t_0) + i_{L1}(t_0)$$

=  $i_{O1}(t) = i_{CB}(t)$  (3)

$$i_{L2}(t) = -\frac{V_O}{L}(t - t_0) + i_{L2}(t_0) = i_{D2}(t)$$

(4)

$$V_{Q2} = V_S \tag{5}$$

$$V_{D1} = V_S - V_{CB} \tag{6}$$

$$V_{CB} \simeq V_{CB}(t_0) + \frac{I_O}{2C_B}(t - t_0).$$

(7)

*Mode 2*  $[t_1-t_2]$ : Mode 2 begins when  $Q_1$  is turned OFF at  $t_1$ . Then,  $i_{L1}(t)$  and  $i_{L2}(t)$  freewheel through  $D_1$  and  $D_2$ ,

respectively. Both  $V_{L1}(t)$  and  $V_{L2}(t)$  become the negative  $V_O$ , and hence,  $i_{L1}(t)$  and  $i_{L2}(t)$  decrease linearly. During this mode, the voltage across  $Q_1$ ,  $V_{Q1}(t)$ , is equal to the difference of  $V_S$ and  $V_{CB}$  and  $V_{Q2}(t)$  becomes  $V_{CB}$ . The voltages and currents can be expressed as follows:

$$V_{L1}(t) = V_{L2}(t) = -V_O$$

(8)

$$i_{L1}(t) = i_{L1}(t_1) - \frac{V_O}{L}(t - t_1) = i_{D1}(t)$$

(9)

$$i_{L2}(t) = i_{L2}(t_1) - \frac{V_O}{L}(t - t_1) = i_{D2}(t)$$

(10)

$$V_{Q1}(t) = V_S - V_{CB}$$

(11)

$$V_{Q2}(t) = V_{CB}.$$

(12)

*Mode 3*  $[t_2-t_3]$ : Mode 3 begins when  $Q_2$  is turned ON at  $t_2$ . At the same time,  $D_2$  is turned OFF. Then,  $i_{L1}(t)$  freewheels through  $D_1$  and  $i_{L2}(t)$  flows through  $D_1$ ,  $C_B$ ,  $Q_2$ , and  $L_2$ . Thus,  $V_{CB}$  is discharged. During this mode,  $V_{L2}(t)$  is equal to the difference of  $V_{CB}$  and  $V_O$  and its level is positive. Hence,  $i_{L2}(t)$  increases linearly.  $V_{L1}(t)$  is the negative  $V_O$ , and hence,  $i_{L1}(t)$  decreases linearly. The voltages and currents can be expressed as follows:

$$V_{L1}(t) = -V_O \tag{13}$$

$$V_{L2}(t) = V_{CB} - V_O (14)$$

$$i_{L1}(t) = \frac{-V_O}{L}(t - t_2) + i_{L1}(t_2)$$

(15)

$$i_{L2}(t) = \frac{V_{CB} - V_O}{L}(t - t_2) + i_{L2}(t_2)$$

=  $i_{O2}(t) = -i_{CB}(t)$  (16)

$$D_{D1}(t) = i_{L1}(t) + i_{L2}(t)$$

(17)

$$V_{O1} = V_S - V_{CB} \tag{18}$$

$$V_{D2} = V_{CB} \tag{19}$$

$$V_{CB} \simeq V_{CB}(t_2) - \frac{I_O}{2C_B}(t - t_2).$$

(20)

*Mode 4*  $[t_3-t_4]$ : Mode 4 begins when  $Q_2$  is turned OFF at  $t_3$ , and its operation is the same with that of mode 2.

The steady-state operation of the proposed IBC operating with the duty cycle of  $D \leq 0.5$  has been described. From the operation principles, it is known that the voltage stress of all semiconductor devices except  $Q_2$  is not the input voltage, but is determined by the voltage of coupling capacitor  $V_{CB}$ . The maximum voltage of  $Q_2$  is the input voltage, but the voltage before turn-on or after turn-off is equal to  $V_{CB}$ . As these results, the capacitive discharging and switching losses on  $Q_1$  and  $Q_2$ can be reduced considerably. In addition, since diodes with good characteristics such as schottky can be used for  $D_1$  and  $D_2$ , the reverse-recovery and conduction losses can be also improved. The loss analysis will be discussed in detail in the next section.

## *B.* Steady-State Operation When D > 0.5

*Mode 1*  $[t_0-t_1]$ : Mode 1 begins when  $Q_2$  is in on-state and  $Q_1$  is turned ON at  $t_0$ . Then,  $i_{L1}(t)$  flows through  $Q_1$ ,  $C_B$ , and  $L_1$  and  $V_{CB}(t)$  is charged.  $i_{L2}(t)$  flows through  $Q_1$ ,  $Q_2$ , and  $L_2$ .  $V_{L1}(t)$  is equal to the difference of  $V_S$ ,  $V_{CB}$ , and  $V_O$  and its level is positive. Thus,  $i_{L1}(t)$  increases linearly from the initial value.  $V_{L2}(t)$  is equal to the difference of  $V_S$  and  $V_O$  and  $i_{L2}(t)$  also increases linearly from the initial value. The voltages and currents can be expressed as follows:

$$V_{L1}(t) = V_S - V_{CB} - V_O \tag{21}$$

$$V_{L2}(t) = V_S - V_O$$

(22)

$$V_{D1} = V_S - V_{CB} \tag{23}$$

$$V_{D2} = V_S \tag{24}$$

$$i_{Q1} = i_{L1}(t) + i_{L2}(t) \tag{25}$$

$$i_{Q2} = i_{L2}(t). (26)$$

*Mode 2*  $[t_1-t_2]$ : Mode 2 begins when  $Q_2$  is turned OFF at  $t_1$ . Then,  $i_{L1}(t)$  flows through  $Q_1, C_B$ , and  $L_1$  and  $i_{L2}(t)$  freewheels through  $D_2$ . The operation during this mode is the same with mode 1 in the case of  $D \le 0.5$ .

*Mode 3*  $[t_2-t_3]$ : Mode 3 begins when  $Q_2$  is turned ON at  $t_2$ , and the operation is the same with mode 1.

*Mode 4*  $[t_3-t_4]$ : Mode 4 begins when  $Q_1$  is turned OFF at  $t_3$ . Then,  $i_{L1}(t)$  freewheels through  $D_1$  and  $i_{L2}(t)$  flows through  $D_1$ ,  $C_B$ ,  $Q_2$ , and  $L_2$ . Thus,  $V_{CB}$  is discharged. The operation during this mode is the same with mode 3 in the case of  $D \le 0.5$ .

The steady-state operation of the proposed IBC operating with D > 0.5 has been described. Under this operating condition, the voltage stress of  $Q_1$  and  $D_1$  is determined by  $V_{CB}$ , but the voltage stress of  $Q_2$  and  $D_2$  is determined by the input voltage. In addition, since  $V_{L2}(t)$  is much larger than  $V_{L1}(t)$  during mode 1 or mode 3, the unbalance between  $i_{L1}(t)$  and  $i_{L2}(t)$  occurs, as shown in Fig. 6. The current of  $Q_1$ ,  $i_{Q1}(t)$ , is the sum of  $i_{L1}(t)$  and  $i_{L2}(t)$  and the current of  $Q_2$ ,  $i_{Q2}(t)$ , is equal to  $i_{L2}(t)$  in mode 1 or mode 3. Therefore, it can be said that switches  $Q_1$  and  $Q_2$  experience high current stress in the case of D > 0.5.

Until now, the steady-state operation of the proposed IBC has been described in detail. Consequently, it can be known that the proposed IBC has advantages in terms of efficiency and component stress in the case of only  $D \le 0.5$ . Thus, the proposed IBC is recommended for the applications where the operating duty cycle is smaller than or equal to 0.5.

#### III. RELEVANT ANALYSIS RESULTS

The proposed IBC will be only employed in the applications where the operating duty cycle is below 0.5, but the following relevant analyses are conducted over the entire duty cycle range for a detail design guide.

## A. DC Conversion Ratio

The dc conversion ratio of the proposed IBC can be derived using the principle of inductor volt-second-balance (VSB) [16].

In the case of  $D \le 0.5$ , the following equations can be obtained from the VSB of  $L_1$  and  $L_2$ , respectively

$$(V_S - V_{CB} - V_O)DT_S = V_O(1 - D)T_S$$

(27)

$$(V_{CB} - V_O)DT_S = V_O(1 - D)T_S.$$

(28)

The voltage of the coupling capacitor can be obtained by substituting (28) into (27) and is equal to half of the input voltage as follows:

$$V_{CB} = \frac{V_S}{2}.$$

(29)

Then, the dc conversion ratio M can be obtained from (27) and (29) or (28) and (29) as follows:

$$M = \frac{V_O}{V_S} = \frac{D}{2}.$$

(30)

In the case of D > 0.5, the voltage of the coupling capacitor and the dc conversion ratio can be obtained by the same procedure and are expressed as follows, respectively

$$V_{CB} = V_S(1-D)$$

(31)

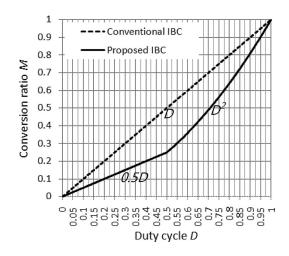

Fig. 6. Key operating waveforms of the proposed IBC when D > 0.5.

$$M = D^2. (32)$$

Fig. 7 shows the curve of M of the proposed IBC. As shown in Fig. 7, the proposed IBC has a higher step-down conversion ratio than the conventional IBC. As a result, the proposed IBC can overcome the extremely short duty cycle, which appears in the conventional IBC.

# B. Inductor Current Ripple

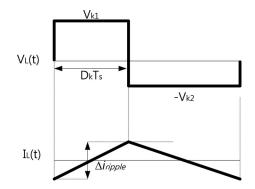

Fig. 8 shows the voltage and current waveforms of the output inductor of the buck converter. From the figure, the current ripple

Fig. 7. DC conversion ratio of the proposed converter.

Fig. 8. Voltage and current waveforms of the output inductor of the buck converter.

can be expressed as follows:

$$\Delta i_{\text{ripple}} = \frac{V_{k1}}{L} D_k T_S \text{ or } \frac{V_{k2}}{L} (1 - D_k) T_S.$$

(33)

In the case of  $D \le 0.5$ , the parameters for the proposed IBC are as follows:

$$V_{k1} = 0.5V_S - V_O, \quad V_{k2} = V_O, \quad D_k = D.$$

(34)

The parameters for the conventional IBC can be expressed as

$$V_{k1} = V_S - V_O, \quad V_{k2} = V_O, \quad D_k = 0.5D.$$

(35)

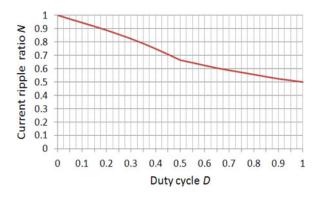

Then, the current ripple ratio *N* of both IBCs can be obtained as follows:

$$N = \frac{\Delta i_{\text{ripple\_proposed}}}{\Delta i_{\text{ripple\_conventional}}} = \frac{1 - D}{1 - 0.5D}.$$

(36)

In the case of D > 0.5, N can be obtained by the same procedure as follows:

$$N = \frac{1}{1+D}.$$

(37)

Fig. 9 shows the curve of *N*. As shown in Fig. 9, the current ripple ratio is smaller than unity. Therefore, it can be said that the proposed IBC has a smaller current ripple than the conventional IBC. Consequently, for the given current ripple specification, the

Fig. 9. Current ripple ratio of the proposed and conventional IBCs.

Fig. 10. Voltage of the coupling capacitor when  $V_S = 200$  V.

inductors with a smaller inductance can be used in the proposed IBC, which results in a faster transient response.

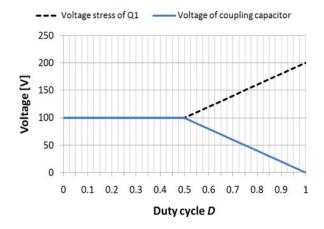

### C. Coupling Capacitor

Fig. 10 shows the voltage of the coupling capacitor when the input voltage is 200 V. As shown in Fig. 10, the voltage is equal to half of the input voltage when the operating duty cycle D is smaller than or equal to 0.5, but decreases linearly as D increases over 0.5. As a result, the voltage stress of  $Q_1$  increases to the input voltage. Thus, we focus on the case of  $D \le 0.5$  from now.

The ripple voltage of the coupling capacitor can be obtained from Fig. 3 as follows:

$$\Delta V_{CB} = \frac{1}{C_B} \int_{t_0}^{t_1} i_{CB}(t) dt = \frac{I_O D}{2C_B f_S}$$

(38)

where

$$i_{CB}(t) = \frac{I_O}{2} - \frac{\Delta i_{\text{ripple}}}{2} + \frac{0.5V_S - V_O}{L}(t - t_0)$$

$$\Delta i_{\text{ripple}} = \frac{0.5V_S - V_O}{L}(t_1 - t_0), \quad t_1 = DT_S + t_0.$$

From (38), it is known that although a capacitor with low capacitance is used for  $C_B$ , the voltage ripple can be reduced by increasing the switching frequency.

TABLE I STRESS ANALYSIS RESULTS AT STEADY STATE

| Items                                    | Proposed IBC                                              | Comparision | Conventional IBC                                       |

|------------------------------------------|-----------------------------------------------------------|-------------|--------------------------------------------------------|

| Voltage stress of Q1                     | $0.5V_s$                                                  | <           | $V_s$                                                  |

| Voltage stress of Q2                     | $V_s$                                                     | =           | $V_{S}$                                                |

| Peak Current stress of Q1&Q2             | $\frac{I_o}{2} + \frac{1}{2} \frac{0.5V_s - V_o}{L} DT_s$ | <           | $\frac{I_o}{2} + \frac{1}{4} \frac{V_s - V_o}{L} DT_s$ |

| RMS current stress of Q1&Q2              | $\frac{I_o}{2}\sqrt{D}$                                   | >           | $\frac{I_o}{2}\sqrt{\frac{D}{2}}$                      |

| Voltage stress of D1&D2                  | $0.5V_S + V_{ringing}$                                    | <           | $V_S + V_{ringing}$                                    |

| Average current stress of $D_1$          | $\frac{I_o}{2}(1-D)$                                      | <           | $\frac{I_o}{2}(1-\frac{D}{2})$                         |

| Average current stress of D <sub>2</sub> | $\frac{I_o}{2}$                                           | >           | $\frac{I_o}{2}(1-\frac{D}{2})$                         |

TABLE II LOSS EQUATIONS AT STEADY STATE

| Items                                                       | Proposed IBC                         | Comparision | Conventional IBC                     |

|-------------------------------------------------------------|--------------------------------------|-------------|--------------------------------------|

| Conduction losses of Q1&Q2                                  | $\frac{I_O^2}{2} DR_{DS_ON}$         | >           | $\frac{I_O^2}{4} DR_{DS_ON}$         |

| Switching losses of Q1&Q2<br>(during turn on/off transiton) | $\frac{V_s I_o}{24} (T_r + T_f) f_s$ | <           | $\frac{V_s I_o}{12} (T_r + T_f) f_s$ |

| Capacitive discharging losses<br>of Q1&Q2                   | $\frac{2}{3}C_{DS}V_S^2f_S$          | <           | $\frac{8}{3}C_{DS}V_S^2f_S$          |

| Conduction losses of D1&D2                                  | $I_O(1-\frac{D}{2})V_F$              | =           | $I_o(1-\frac{D}{2})V_F$              |

The RMS value of the current through the coupling capacitor can be obtained as follows:

$$I_{CB\_RMS} = \sqrt{\frac{2}{T_S}} \int_{t_0}^{t_1} i_{CB}^2(t) dt \simeq \frac{I_O}{2} \sqrt{2D}.$$

(39)

This means that the capacitor for  $C_B$  should have a high current-carrying capability. However, since the use of a much higher number of phases in parallel can reduce the RMS current stress of  $C_B$ , it does not become a severe disadvantage.

### D. Stress and Loss Analysis

For stress and loss analysis, it is assumed that the IBCs operate with the duty cycle of  $D \le 0.5$ .

The results of stress analysis can be summarized as in Table I.

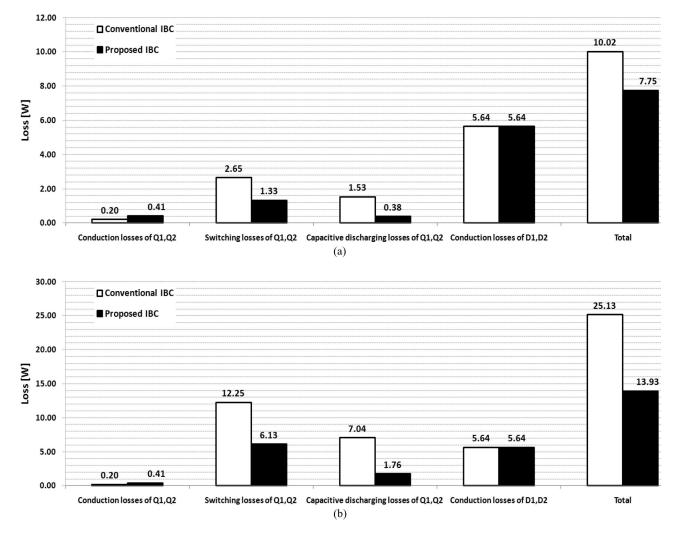

Equations for loss analysis can be obtained by referring [3], [11], [17], [18] and can be summarized as in Table II. For quantitative loss analysis, the parameters given next are used:

- 1) input voltage:  $V_S = 200 \text{ V}$ ;

- 2) output voltage:  $V_O = 24$  V;

- 3) output current:  $I_O = 10 \text{ A}$ ;

- 4) switching frequency :  $f_S = 65 \text{ kHz}$  or 300 kHz;

- 5) switches for  $Q_1$  and  $Q_2$ : FQPF16N25C ( $C_{\rm DS} = 220$  pF,  $R_{\rm DS\_ON} = 0.27 \ \Omega, T_r = 270$  ns,  $T_f = 220$  ns);

- 6) diodes for  $D_1$  and  $D_2$ : FFPF10UP30S ( $V_F = 1.2$  V).

Fig. 11 shows the results of loss analysis. From Fig. 11, it is investigated that due to the improved voltage waveforms in the proposed IBC, the capacitive discharging and switching losses are reduced. Also, it can be seen that at higher switching frequency, the increased losses in the proposed IBC are much smaller than those in the conventional IBC. This means that the proposed converter can operate at higher switching frequencies

Fig. 11. Loss analysis results. (a) At 65 kHz. (b) At 300 kHz.

without the penalty of a significant increase in the losses. Thus, it can be said that the propose IBC is more advantageous in terms of efficiency and power density compared with the conventional IBC.

At this loss analysis, the losses related to the output inductors, the reverse recovery of  $D_1$  and  $D_2$ , and the gate driving circuits are not considered.

## E. Transient Voltage Stress

In the conventional IBC, the voltage stress of the freewheeling diodes is much higher than the input voltage due to the ringing caused by parasitic elements during the startup or in the steady state. Thus, high-voltage diodes rated above the input voltage should be used as the freewheeling diodes.

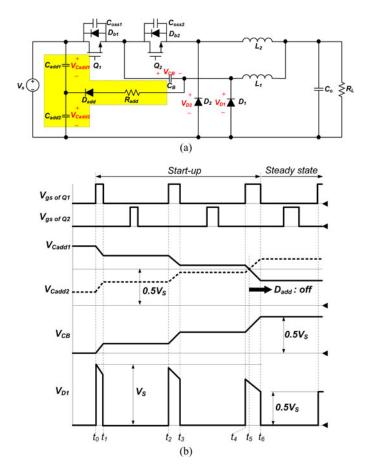

On the other hand, in the proposed IBC, the voltage stress of  $D_1$  is the difference of the input voltage  $V_S$  and the voltage of the coupling capacitor  $V_{CB}$ , and the voltage stress of  $D_2$  is  $V_{CB}$ . In the steady state,  $V_{CB}$  is  $0.5V_S$  and the voltage stress of  $D_1$  and  $D_2$  becomes  $0.5V_S$ . However, since  $V_{CB}$  increases from zero during the cold startup, the voltage stress of  $D_1$  decreases from  $V_S$  to  $0.5V_S$ , and the voltage stress of  $D_2$  increases from zero to  $0.5V_S$ . Consequently, considering the ringing caused by parasitic elements, the voltage stress of  $D_2$  is always below the input voltage, but the voltage stress of  $D_1$  could be higher than the input voltage.

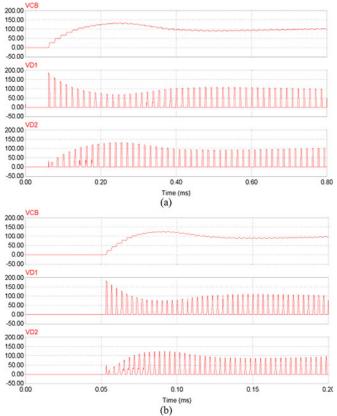

For the reduction of the transient voltage stress of  $D_1$ , an auxiliary circuit that is composed of two capacitors, a diode, and a resister is added to the input stage of the proposed IBC, as shown in Fig. 12(a). Fig. 12(b) shows the operating waveforms during the cold startup. As shown in Fig. 12(b), the circuit absorbs the transient energy generated by parasitic elements during the cold startup and quickly charges  $V_{CB}$ . Then, the voltage of  $D_1$  is also quickly reduced below the input voltage. That is, after employing the auxiliary circuit, the voltage of  $D_1$ cannot be above the input voltage. This can be confirmed by the simulation results shown in Fig. 13. Thus, lower voltage diodes can be employed for  $D_1$  and  $D_2$  compared with conventional IBC.

Additionally, the auxiliary circuit works during only the cold startup and does not affect the steady-state operation of the proposed IBC.

Fig. 12. (a) Proposed IBC with the auxiliary circuit for the reduction of the transient voltage stress of  $D_1$ . (b) Its operating waveforms during cold start-up.

#### **IV. EXPERIMENTAL RESULTS**

The proposed and conventional IBCs are realized with the specifications shown next.

- 1) Input voltage:  $V_S = 150-200$  V.

- 2) Output voltage:  $V_O = 24$  V.

- 3) Output current:  $I_O = 10$  A.

- 4) Switching frequency:  $f_S = 65 \text{ kHz}$  or 300 kHz.

- 5) Inductor ripple current: below 3 A.

- 6) Ripple voltage of a coupling capacitor: below 4 V.

- 7) Output voltage ripple: below 250 mV.

The prototypes for the experiment, which are the conventional IBC and proposed IBCs, have been built and tested to verify the operational principle, advantages, and performances of the proposed IBC, using the components as shown in Table III. In order to alleviate the ringing caused by parasitic elements, two simple RC snubbers are used across diodes  $D_1$  and  $D_2$ , respectively. Their values are as follows:

$$R = 10 \ \Omega/1 \,\mathrm{W}, C = 10 \ \mathrm{nF}/630 \,\mathrm{V}.$$

For the experiment of the proposed IBC2, which is the proposed IBC with lower voltage rated freewheeling diodes, the auxiliary circuit described in Section III is added. The

Fig. 13. Simulation results of the proposed IBC with the auxiliary circuit during cold start-up when  $V_S = 200$  V. (a) At  $f_S = 65$  kHz. (b) At  $f_S = 300$  kHz.

TABLE III Components List

| Items                                         | Conventional IBC                                                                                                                  | Proposed IBC1                                 | Proposed IBC2                 |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------|--|

| Main diodes (D <sub>1</sub> ,D <sub>2</sub> ) | FFPF10UP30S<br>*Ultra fast recovery diode                                                                                         | FFPF10UP30S<br>*Ultra fast recovery diode     | MBR20200CT<br>*Schottky diode |  |

| Coupling capacitor (C <sub>B</sub> )          | -                                                                                                                                 | 4µF/250V at f₅=65kHz<br>1µF/250V at f₅=300kHz |                               |  |

| Main switches (Q1,Q2)                         | FQPF16N25C                                                                                                                        |                                               |                               |  |

| Inductors (L <sub>1</sub> ,L <sub>2</sub> )   | PQ3230 (22mm-32mm-30mm), 0.05mm-245, 19turns, 100µH at fs=65kHz<br>PQ2620 (19mm-26mm-20mm), 0.05mm-245, 6turns, 20µH at fs=300kHz |                                               |                               |  |

| Output capacitor (Co)                         | 22μF/50V at ß=65kHz<br>3μF/50V at ß=300kHz                                                                                        |                                               |                               |  |

components are as follows:

$$\begin{split} C_{\mathrm{add1}} &= C_B, \quad C_{\mathrm{add2}} = 2C_B, \\ R_{\mathrm{add}} &= 3\,\Omega/0.25\,\mathrm{W}, \quad D_{\mathrm{add}} = \mathrm{UF4004} \times 2. \end{split}$$

### A. Waveforms

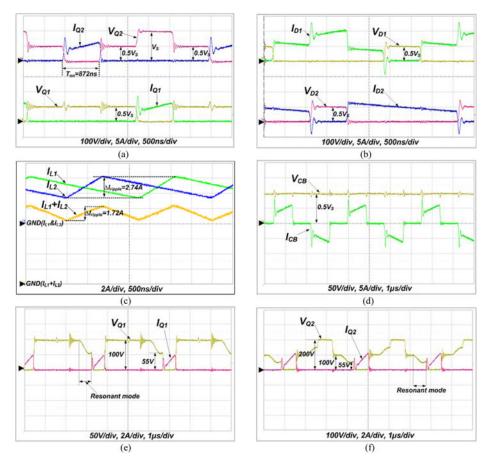

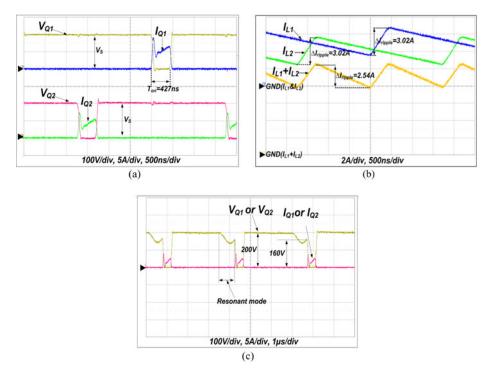

Figs. 14 and 15 show the experiment waveforms of the proposed IBC1 and conventional IBC, respectively. As shown in Figs. 14(a) and 15(a), the conventional IBC has the voltage waveforms of the input voltage level, but the proposed IBC has the improved voltage waveforms, as discussed in the circuit operation. This allows the capacitive discharging and switching losses to be reduced. In addition, when the input voltage is 200 V, the conventional IBC has a very short on-time, and hence, two inductor currents are unbalanced, as shown in Fig. 15(b). To

Fig. 14. Experimental waveforms of the proposed IBC1 when  $V_S = 200$  V and  $f_S = 300$  kHz. (a) Currents and voltages of  $Q_1$  and  $Q_2$  at  $I_O = 10$  A. (b) Currents and voltages of  $D_1$  and  $D_2$  at  $I_O = 10$  A. (c) Currents of  $L_1$  and  $L_2$  at  $I_O = 10$  A. (d) Current and voltage of the coupling capacitor at  $I_O = 10$  A. (e) Current and voltage of  $Q_1$  at  $I_O = 2$  A. (f) Current and voltage of  $Q_2$  at  $I_O = 2$  A.

Fig. 15. Experimental waveforms of a conventional IBC when  $V_S = 200$  V and  $f_S = 300$  kHz. (a) Currents and voltages of  $Q_1$  and  $Q_2$  at  $I_O = 10$  A. (b) Currents of  $L_1$  and  $L_2$  at  $I_O = 10$  A. (c) Current and voltage of  $Q_1$  or  $Q_2$  at  $I_O = 2$  A.

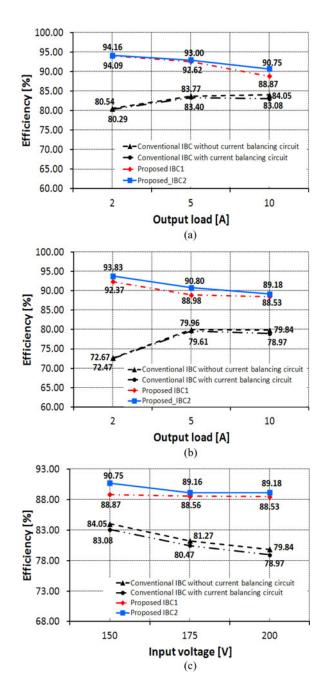

Fig. 16. Efficiencies at  $f_S = 65$  kHz. (a)  $V_S = 150$  V. (b)  $V_S = 200$  V. (c)  $I_O = 10$  A.

solve this problem, the conventional IBC needs the additional current balancing circuit, which increases the circuit complexity and generates the power loss. On the other hand, the proposed IBC has twice the on-time of the conventional IBC under the same input voltage condition. Hence, two inductor currents are well autobalanced without any additional current balancing circuits. Fig. 14(b) shows the voltage and current waveforms of the freewheeling diodes. As shown in Fig. 14(b), the voltages are half of the input voltage. Thus, schottky diodes that have generally lower breakdown voltages, typically below 200 V, can be used as the freewheeling diodes if the voltage stress of  $D_1$  is below the input voltage during the cold startup. Since schottky diodes have good characteristics such as low forward voltage

Fig. 17. Efficiencies at  $f_S = 300$  kHz. (a)  $V_S = 150$  V. (b)  $V_S = 200$  V. (c)  $I_O = 10$  A.

drop and no reverse recovery, the efficiency of the proposed IBC will be further improved. Fig. 14(d) shows the voltage and current waveforms of the coupling capacitor. As shown in Fig. 14(d), the voltage is constant with the half of the input voltage. Figs. 14(c) and 15(b) show the inductor current waveforms. From Figs. 14(c) and 15(b), it can be seen that the proposed IBC has a smaller current ripple than the conventional IBC.

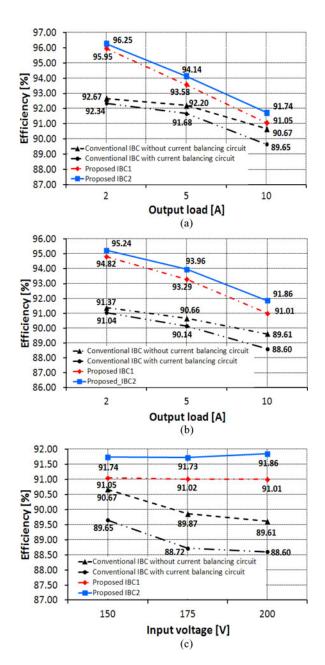

# B. Efficiency

Figs. 16 and 17 show the efficiency measured by a power analyzer (PM3000A, Voltech) when the switching frequency is 65 or 300 kHz, respectively. For efficiency comparison, the

unbalanced current in the conventional IBC was corrected by the additional current balancing circuit using two sensing resistors. Figs. 16(a) and 17(a) or 16(b) and 17(b) show the efficiencies under different load conditions at 150 or 200 V input voltage, respectively. Figs. 16(c) and 17(c) show the efficiencies under different input voltages at the load condition of 10 A.

From the efficiency in Figs. 16 and 17, we can know that the proposed IBC has a higher efficiency than the conventional IBC because of the improved voltage waveforms and no use of the extra current balancing circuit. Moreover, the improvement in the efficiency gets larger as the switching frequency increases. Especially, it is more pronounced under light-load conditions. This is explained with Fig. 14(e) and (f), and 15(c). As the load current decreases, all IBCs enter into DCM. If the inductor current becomes zero in DCM, the resonance between the junction capacitances of all semiconductor devices and the output inductors occurs so that the active switches are turned ON with lower voltage level, as shown in Figs. 14(e)-(f), and 15(c). Here, we can know that the voltage level of the proposed IBC at a turn-on transient time is much lower than that of the conventional IBC from the experiment waveforms. This means that the capacitive discharging and switching losses are further improved.

Additionally, from the efficiency of the proposed IBC2 in Figs. 16 and 17, it is seen that the efficiency of the proposed IBC is further improved after employing schottky diodes.

## V. CONCLUSION

A new IBC is proposed in this paper. While keeping the good characteristics of the IBC introduced in [14], it has a more simple structure. The main advantage of the proposed IBC is that since the voltage stress across active switches is half of the input voltage before turn-on or after turn-off when the operating duty is below 50%, the capacitive discharging and switching losses can be reduced considerably. In addition, since the voltage stress of the freewheeling diodes is half of the input voltage in the steady state and can be quickly reduced below the input voltage during the cold startup, the use of lower voltage-rated diodes is allowed. Thus, the losses related to the diodes can be improved by employing schottky diodes that have generally low breakdown voltages, typically below 200 V. From these results, the efficiency of the proposed IBC is higher than that of the conventional IBC and the improvement gets larger as the switching frequency increases. These are verified with the experimental results. Moreover, it is confirmed that the proposed IBC has a higher step-down conversion ratio and a smaller inductor current ripple than the conventional IBC. Therefore, the proposed IBC becomes attractive in applications where nonisolation, step-down conversion ratio with high input voltage, high output current with low ripple, higher power density, and low cost are required.

### REFERENCES

P. L. Wong, P. Xu, B. Yang, and F. C. Lee, "Performance improvements of interleaving VRMs with coupling inductors," *IEEE Trans. Power Electron.*, vol. 168, no. 4, pp. 499–507, Jul. 2001.

- [2] R. L. Lin, C. C. Hsu, and S. K. Changchien, "Interleaved four-phase buck-based current source with isolated energy-recovery scheme for electrical discharge machine," *IEEE Trans. Power Electron.*, vol. 24, no. 7, pp. 2249–2258, Jul. 2009.

- [3] C. Garcia, P. Zumel, A. D. Castro, and J. A. Cobos, "Automotive DC–DC bidirectional converter made with many interleaved buck stages," *IEEE Trans. Power Electron.*, vol. 21, no. 21, pp. 578–586, May 2006.

- [4] J. H. Lee, H. S. Bae, and B. H. Cho, "Resistive control for a photovoltaic battery charging system using a microcontroller," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2767–2775, Jul. 2008.

- [5] Y. C. Chuang, "High-efficiency ZCS buck converter for rechargeable batteries," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2463–2472, Jul. 2010.

- [6] C. S. Moo, Y. J. Chen, H. L. Cheng, and Y. C. Hsieh, "Twin-buck converter with zero-voltage-transition," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2366–2371, Jun. 2011.

- [7] X. Du and H. M. Tai, "Double-frequency buck converter," *IEEE Trans. Ind. Electron.*, vol. 56, no. 54, pp. 1690–1698, May 2009.

- [8] K. Jin and X. Ruan, "Zero-voltage-switching multiresonant three-level converters," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1705–1715, Jun. 2007.

- [9] J. P. Rodrigues, S. A. Mussa, M. L. Heldwein, and A. J. Perin, "Threelevel ZVS active clamping PWM for the DC–DC buck converter," *IEEE Trans. Power Electron.*, vol. 24, no. 10, pp. 2249–2258, Oct. 2009.

- [10] X. Ruan, B. Li, Q. Chen, S. C. Tan, and C. K. Tse, "Fundamental considerations of three-level DC–DC converters: Topologies, analysis, and control," *IEEE Trans. Circuit Syst.*, vol. 55, no. 11, pp. 3733–3743, Dec. 2008.

- [11] Y. M. Chen, S. Y. Teseng, C. T. Tsai, and T. F. Wu, "Interleaved buck converters with a single-capacitor turn-off snubber," *IEEE Trans. Aerosp. Electronic Syst.*, vol. 40, no. 3, pp. 954–967, Jul. 2004.

- [12] C. T. Tsai and C. L. Shen, "Interleaved soft-switching coupled-buck converter with active-clamp circuits," in *Proc. IEEE Int. Conf. Power Electron.* and Drive Systems., 2009, pp. 1113–1118.

- [13] M. Ilic and D. Maksimovic, "Interleaved zero-current-transition buck converter," *IEEE Trans. Ind. App.*, vol. 43, no. 6, pp. 1619–1627, Nov. 2007.

- [14] K. Yao, Y. Qiu, M. Xu, and F. C. Lee, "A novel winding-coupled buck converter for high-frequency, high-step-down DC–DC conversion," *IEEE Trans. Power Electron.*, vol. 20, no. 5, pp. 1017–1023, Sep. 2005.

- [15] K. Yao, M. Ye, M. Xu, and F. C. Lee, "Tapped-inductor buck converter for high-step-down DC–DC conversion," *IEEE Trans. Power Electron.*, vol. 20, no. 4, pp. 775–780, Jul. 2005.

- [16] R. W. Erickson and D. Maksimović, Fundamentals of Power Electronics: Kluwer Academic Publisher, 2001, pp. 15–22.

- [17] J. Y. Lee, Y. S. Jeong, and B. M. Han, "An isolated DC/DC converter using high-frequency unregulated LLC resonant converter for fuel cell applications," *IEEE Trans. Ind. Electron.*, vol. 58, no. 7, pp. 2926–2934, Jul. 2011.

- [18] R. W. Erickson and D. Maksimović, Fundamentals of Power Electronics: Kluwer Academic Publisher, 2001, pp. 78–100.

**II-Oun Lee** (S'10) was born in Korea in 1976. He received the B.S degree in electrical and electronic engineering from Kyungpook National University, Taegu, Korea, in 2000 and the M.S. degree in electrical engineering from Seoul National University, Seoul, Korea, in 2002. He is currently working toward the Ph.D. degree at the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea.

Beginning in 2003, he was a Research Engineer in the plasma display panel (PDP) Development Group, Samsung SDI, Korea, for five years, where he was

involved in circuit and product development for 42-in, 50-in, 63-in, and 80-in PDP TV. From 2008 to 2009, he was a Senior Engineer in the Power Advanced Development Group, Samsung Electro-Mechanics Co. Ltd., where he was involved in the power circuit development for LED lighting, LCD TV, PDP TV, and server power system. His current research interests include dc–dc converters, power-factor-correction ac–dc converters, LED driver, battery charger for electric vehicle, digital display power systems, and digital control approach of dc–dc converters.

Shin-Young Cho (S'10) was born in Seoul, Korea, in 1981. He received the B.S degree in electrical engineering from Hanyang University, Seoul, in 2007, and the M.S degree in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2010, where he is currently working toward the Ph.D. degree.

His research interests are in the areas of power electronics: display driver system and on-board charger for electric vehicle including the analysis, modeling, design, and control of power converters.

**Gun-Woo Moon** (S'92–M'00) received the M.S. and Ph.D. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 1992 and 1996, respectively.

He is currently a Professor in the Department of Electrical Engineering, KAIST. His research interests include modeling, design, and control of power converters, soft-switching power converters, resonant inverters, distributed power systems, power-factor correction, electric drive systems, driver circuits of plasma display panels, and flexible ac transmission systems.

Dr. Moon is a member of the Korean Institute of Power Electronics, the Korean Institute of Electrical Engineers, the Korea Institute of Telematics and Electronics, the Korea Institute of Illumination Electronics and Industrial Equipment, and the Society for Information Display.